Einleitung

Test

Funktionsprinzip

Eigentümlichkeiten

Überlegungen zum Bau

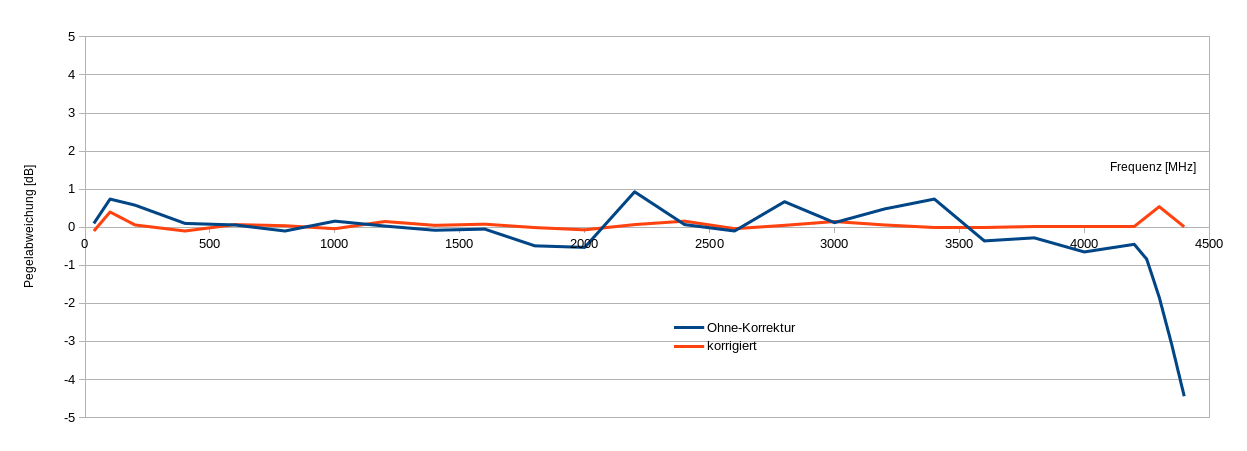

Signalpegel-Linearisierung

Projektstatus

Downloads

zurück zu Projekte

zurück zu HF

Einleitung Test Funktionsprinzip Eigentümlichkeiten Überlegungen zum Bau Signalpegel-Linearisierung Projektstatus Downloads zurück zu Projekte |

|

|

|

|

|

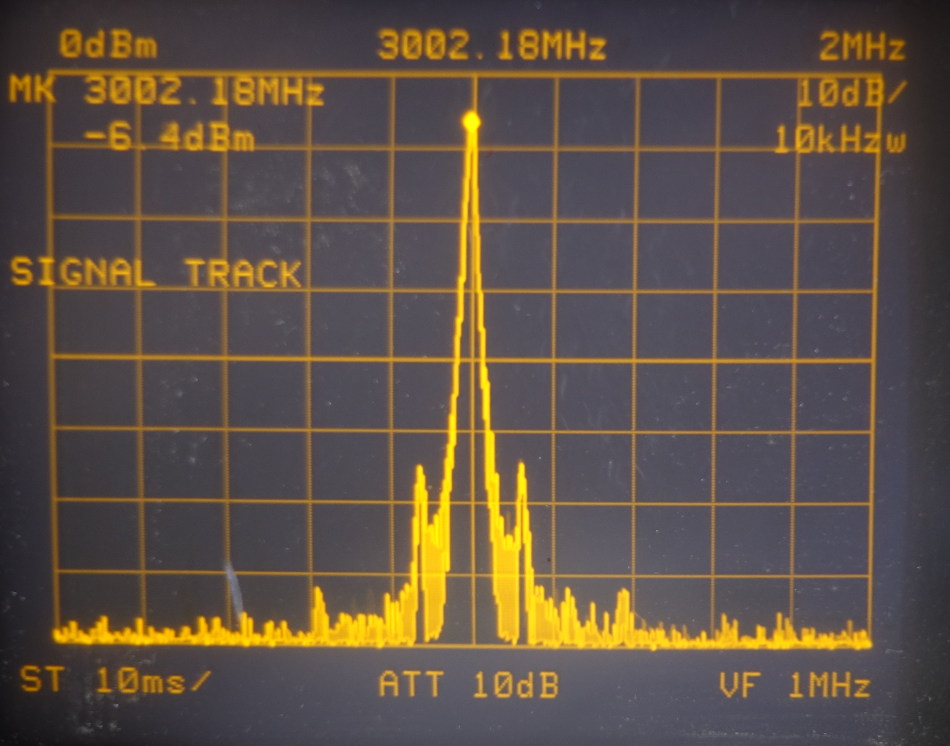

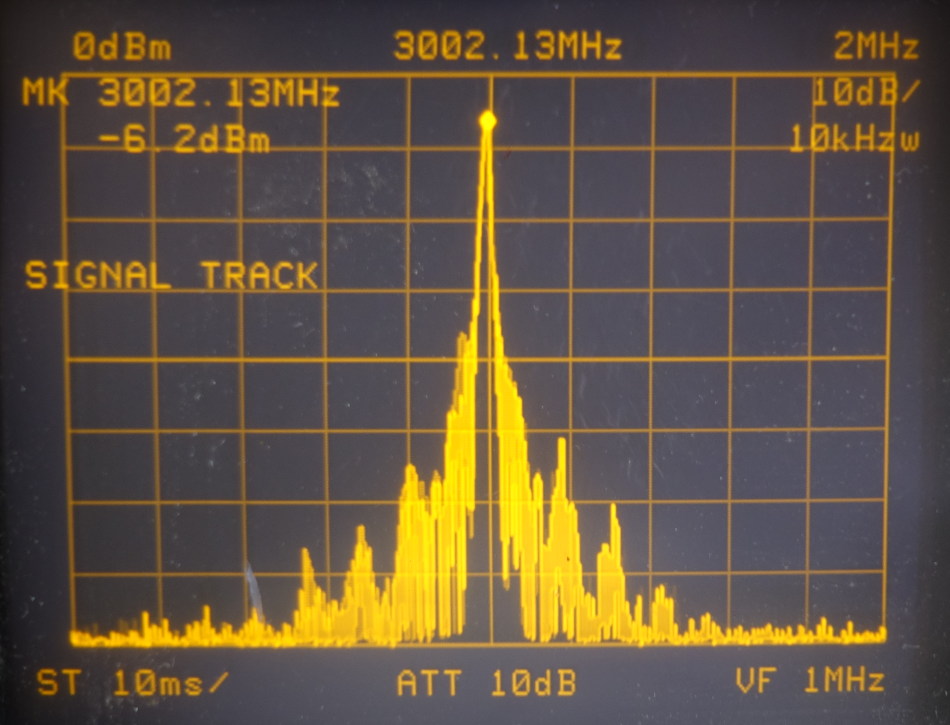

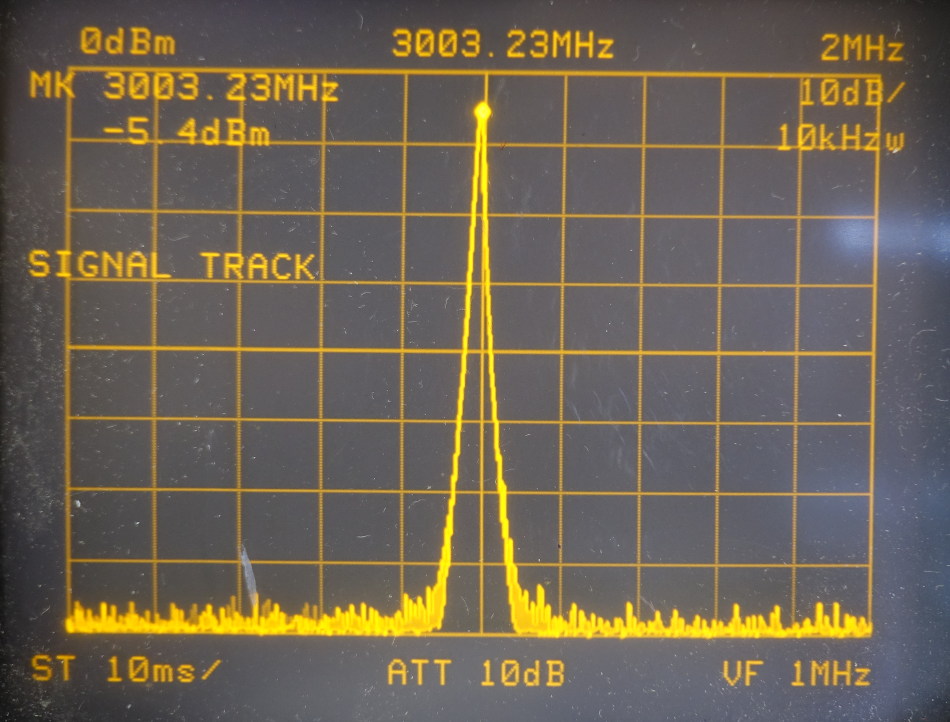

| INT-Mode | FRAC-Mode. | Agilent 8648 zum Vergleich |

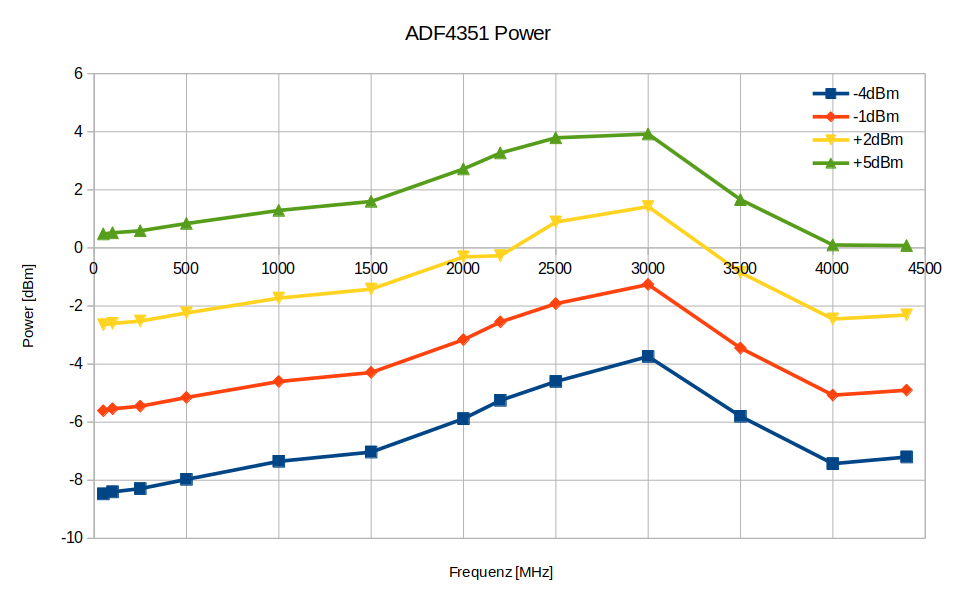

Ausgangsleistung des ADF4351 |

| Frequenz |

200 MHz |

400 MHz |

700 MHz |

1 GHz |

2 GHz |

3 GHz |

4 GHz |

| Dämpung bei Output-Off |

>60 dB |

54 dB |

50 dB |

48 dB |

43 dB |

36 dB |

47 dB |

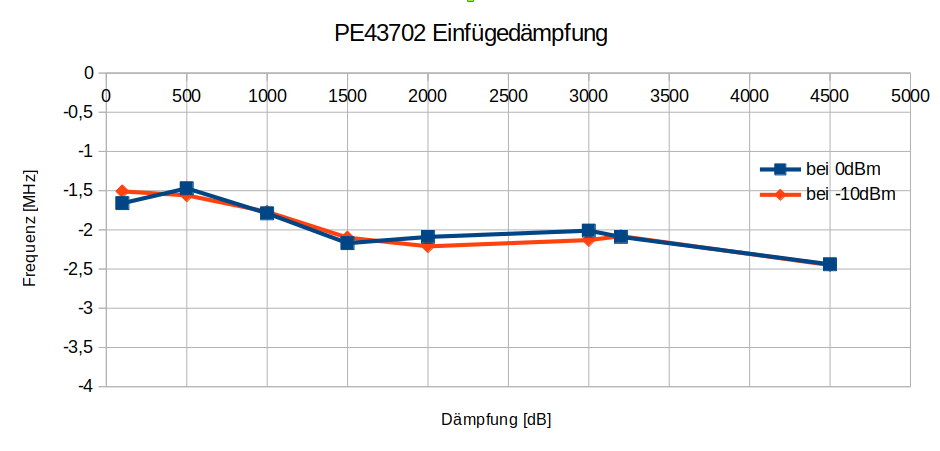

| Man kann aber eine Linearisierung der

Ausgangsleistung erreichen, wenn man ihm einen elektronisch

einstellbaren Abschwächer

mit dem PE43702 nachschaltet. Dessen Ansteuerung kann mit dem selben SPI-Interface erfolgen, das auch den ADF4351 steuert, man benötigt lediglich eine zusätzliche IO-Leitung, die den Ladeimpuls des Schieberegisters erzeugt. Der Betrieb von ADF4351 und PE43702 am gemeinsamen SPI-Interface eines USB4ALL wurde getestet. Die nebenstehende Grafik zeigt die gemessene Grunddämpfung (Einstellung: 0dB) für verschiedene Eingangspegel von 500 MHz bis 4,5 GHz. (Mit +10dBm habe ich nur bis 3,2 GHz gemessen.) Die von mir gemessene Einfügedämpfung des PE42702 änderte sich von 100 MHz bis zu 3 GHz nur um etwa 0,5 dB. Bei höheren Frequenzen hatte ich einige messtechnische Probleme, aber bis 4,5 GHz stellte ich nur ein weiteres halbes dB Dämpfung fest. Das ist für den geplanten Einsatzzweck völlig ausreichend. |

|

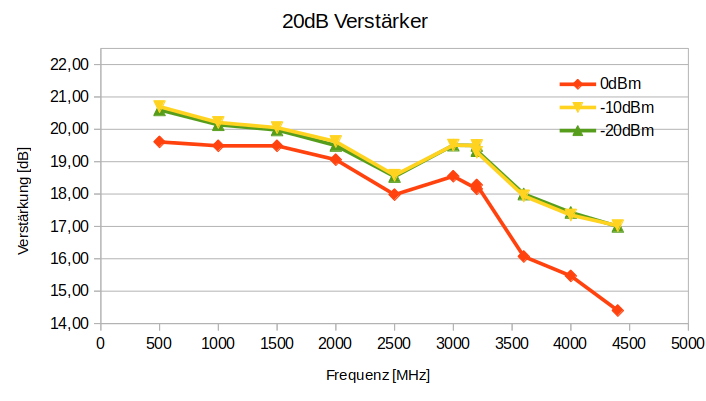

| Dem Leistungsproblem kann man mit einem 20 dB Verstärker begegnen.

Dessen Verstärkung/Gain verringert sich aber im Bereich von

2 bis 4 GHz auch um 5 dB (von 20 auf 15 dB), sein

Frequenzgang ist also noch deutlich schlechter als der des

ADF4351. Auch das muss wieder vom PE43702 ausgeglichen

werden. Die Grafik zeigt die gemessene Verstärkung für verschiedene Eingangsleistungen im Frequenzbereich bis 4,4 GHz. Sie macht auch klar, dass die Eingangsleistung des Verstärkers deutlich unter 0 dBm bleiben muss, um die Sättigung zu vermeiden (rote Linie). Hält man sich daran, dann ist die Verstärkung mit 17dB bei 4,4 GHz besser als vom Datenblatt versprochen. Die maximale Ausgangsleistung, die von der Kette aus ADF4351, PE43702 und Verstärker im gesamten Bereich 2,2 ... 4,4 GHz immer sicher erreicht werden kann, ist +15 dBm. Der Wert auf den sich die Leistung in jedem Falle immer reduzieren lässt ist -20 dBm. |

|

| input: Freq_Mhz die Sollfrequenz, die erzeugt werden soll Quarz_Mhz die Frequenz des verbauten Quarzes in MHz kann 10 oder 25 sein // zuerst berechnet man RF_DIV (ganzzahlig) // und merkt sich das Zwischenergebnis DIV_SET (ganzzahlig) RF_DIV := round( log2(2200 / Freq_MHz) + 0.5) RF_DIV := MAX( RF_DIV , 0) RF_DIV := MIN( RF_DIV , 8) DIV_SET := RF_DIV RF_DIV := round(power(2, RF_DIV)) // T und D steuern den Frequenzhalbierer und den Verdoppler // sie können 0 oder 1 sein T := 1 D := 0 // nun lege ich einen passenden Wert für R fest, der muss zur Quarzfrequenz passen // wenn ein 25MHz-Quarz verwendet wird dann: R := 100 Quarz_MHz := 25 //wenn aber ein 10MHz-Quarz verwendet wird dann: R := 50 Quarz_MHz := 10 // nun bestimme ich den Anstand zwischen zwei Frequenzen im INT-Mode Step_MHZ := ((1+D)/(R*(1+T))) * Quarz_MHz; // 25->0,02 10->0,005 // und nun folgen die ganzzahligen Parameter INT, MODO und FRAC // dabei wird der Gleitkommawert INT_f ermittelt INT_f := (Freq_Mhz / Step_MHz) * RF_DIV; INT := TRUNC(INT_f); MODO := 4000; FRAC := round( (INT_f - INT) * MODO); // es erfolgt die Bestimmung der wirklich erzielten Ausgangsfrequenz // die kann einen Hauch vom Sollwert abweichen, da die Frequenz in Stufen eingestellt wird // den Wert kann man z.B. auf einem Display anzeigen Fout := Step_MHZ * ( INT + (FRAC / MODO)) * 1000 / RF_DIV; // nun werden die sechs 32-Bit-Werte ermittelt, // die dann per SPI in den Chip geschrieben werden müssen adf[0] := (INT shl 15) or (FRAC shl 3) adf[1] := 1 or (MODO shl 3) or (1 shl 27) adf[2] := 0x0C002E42 or (R shl 14) or (T shl 24) or (D shl 25) adf[3] := 0x00010033 adf[4] := 0x000C8024 or (1 shl 23) or (DIV_SET shl 20) adf[5] := 0x00580005 // falls FRAC zufällig 0 sein sollte, lässt sich noch was optimieren if FRAC=0 then begin adf[2] := adf[2] or (1 shl 8) adf[3] := adf[3] or (1 shl 21) or (1 shl 22) end; // P_SET ist die Ausgangsleistungsstufe von 0=-4dBm; 1=-1dBm; 2=+2dBm; 3=+5dBm; adf[4] := adf[4] or (P_SET shl 3) //fertig, nun können adf[0] ... adf[5] in umgekehrter Reihenfolge den Chip geschrieben werden |

|

4 321.654 987 MHz -2.20 dBm 603 uW INT OFF Pow MHz kHz QCal |

|

4 321.654 987 MHz -2.20 dBm 603 uW INT OFF Frq +dBm -dBm PCal |

|

4 321.654 987 MHz -2.20 dBm 603 uW INT 0 ON Save P+ P- Back |

|

4 321.654 987 MHz -2.20 dBm 603 uW INT 25 000 000 ON Save +MHz -MHz Back |

Autor: sprut

geändert: 24.07.2021

erstellt: 16.02.2019